William Stallings Computer Organization and Architecture 8<sup>th</sup> Edition

**Chapter 3 Visão Superior do Computador**

### O que é um software

- Uma sequência de passos

- Para cada passo, uma operação lógica ou aritmética é realizada

- Para cada operação, um conjunto de sinais de controle é necessário

### Função da Unidade de Controle

- Para cada operação, é chamada um código único

- -Ex.: ADD, MOVE

- Um segmento de hardware aceita esse código e lança sinais de controle

- Nós temos um computador!

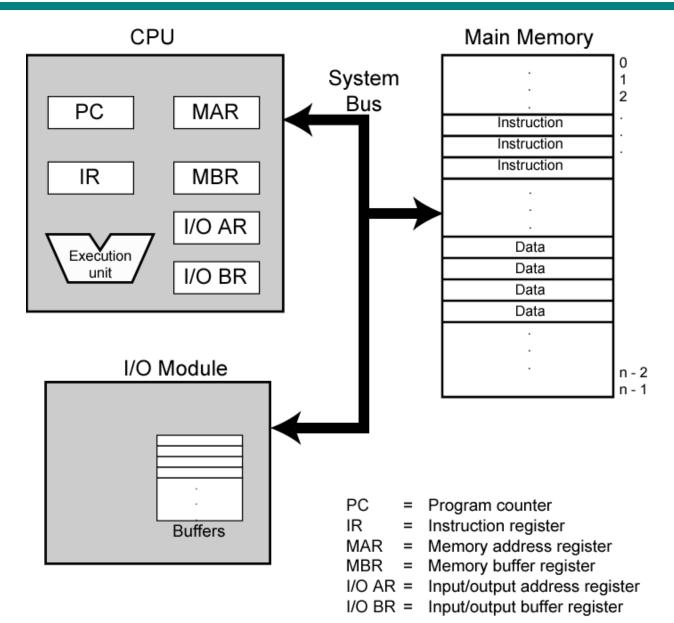

### Componentes

- A Unidade de Controle (UC) e a Unidade Lógica e Aritmética (ULA) formam a Unidade Central de Processamento (UCP) ou Central Processing Unity (CPU)

- Dados e instruções precisam entrar no Sistema e os resultados devem sair

- —Entrada/Saída (E/S)

- É necessário Armazenamento temporário do Código e dos resultados

- -Memória Principal

# **Computer Components: Top Level View**

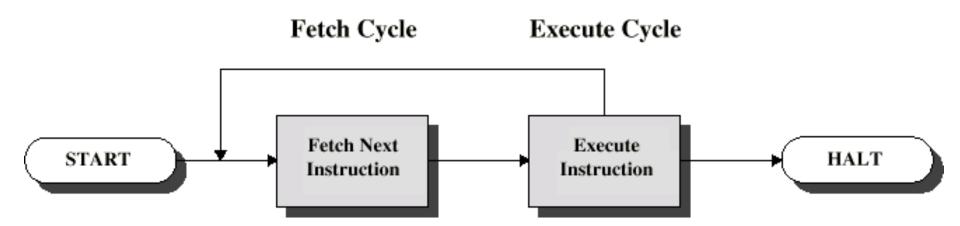

### Ciclo de Instrução

- Dois passos:

- -Busca

- -Execução

### Ciclo de Busca

- Contador de Programa Program Counter (PC) – armazena o endereço da próxima instrução

- Processador busca instrução na memória, no endereço armazenado no PC

- Incrementa o PC

- —A menos que se solicite algo diferente

- Instrução é armazenada no Registrador de Instrução - Instruction Register (IR)

- Processador insterpreta a instrução e realiza a ação solicitada

### Ciclo de Execução

- Processador Memória

- Dado transferido entre CPU e Memória

Principal

- Processador E/S

- —Dado transferido entre CPU e modulo E/S

- Processamento de Dados

- Alguma operação lógica ou aritmética nos dados

- Controle

- Mudança na sequência lógica de execução

- —Ex.: jump / branch

- Combinação deles

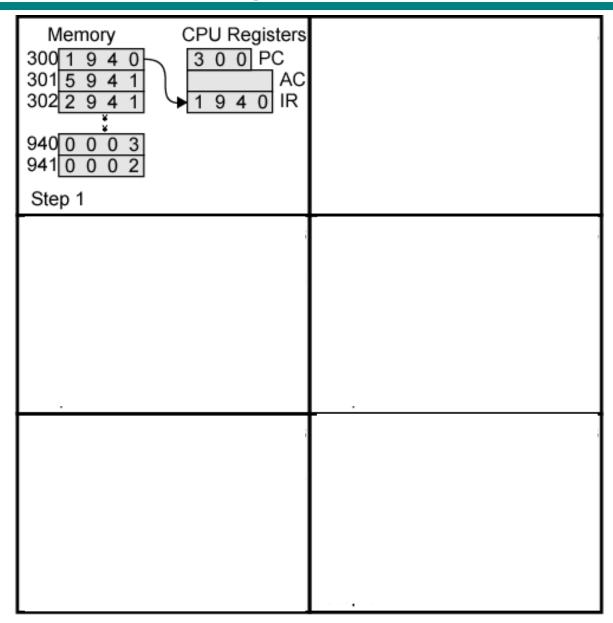

### Exemplo de Execução em Baixo Nível

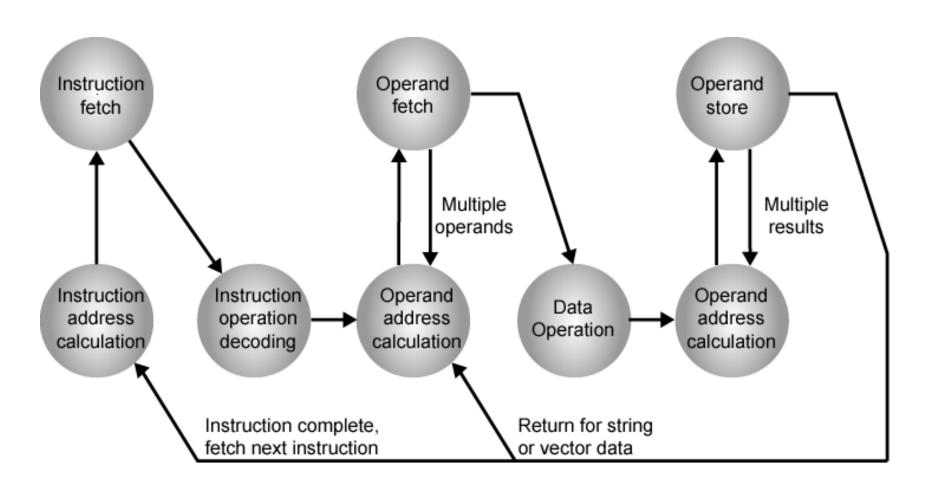

# Diagrama de Estados do Ciclo de Instrução

### Interrupções

- Mecanismos pelo qual outros módulos (Ex.: E/S) pode interromper a sequência normal de processamento

- Programa

- —Ex.: Estouro de Memória, Divisão por zero

- Tempo

- Gerado por temporizador interno da CPU

- -Usado em multitarefa preemptiva

- E/S

- —Do controlador de E/S

- Falha de Hardware

- —Ex.: Erro de paridade de memória

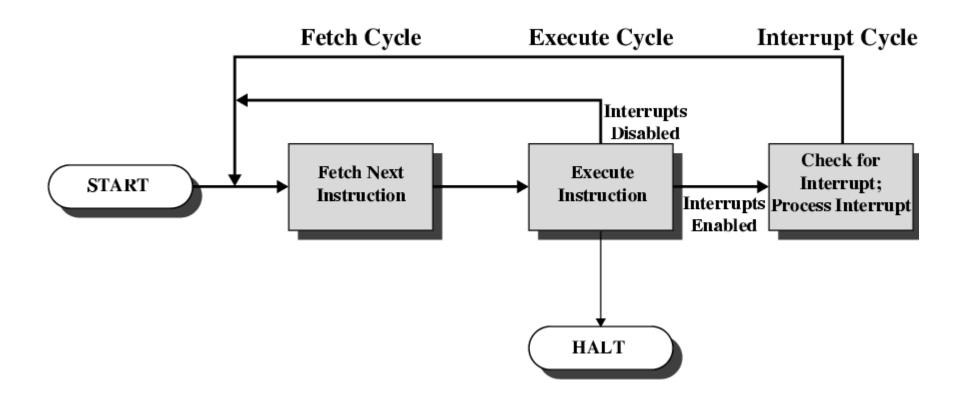

### Ciclo de Interrupção

- Adicionado ao ciclo de instrução

- Processador verifica interrupção

- Indicado por um sinal de interrupção

- Se não houver interrpção, vai para a póxima instrução

- Se houver interrupção:

- Suspende a execução da aplicação

- Salva o contexto

- Coloca no Contador de Programas o endereço inicial para o tratamento da interrupção

- Interrompe o processo

- Restaura o contexto e continua na aplicação que foi anteriormente interrompida

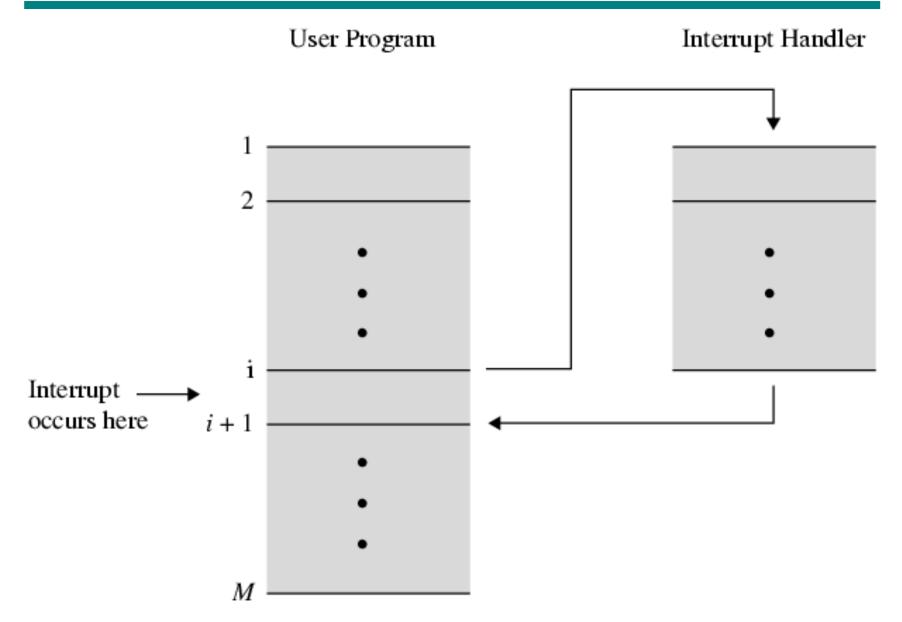

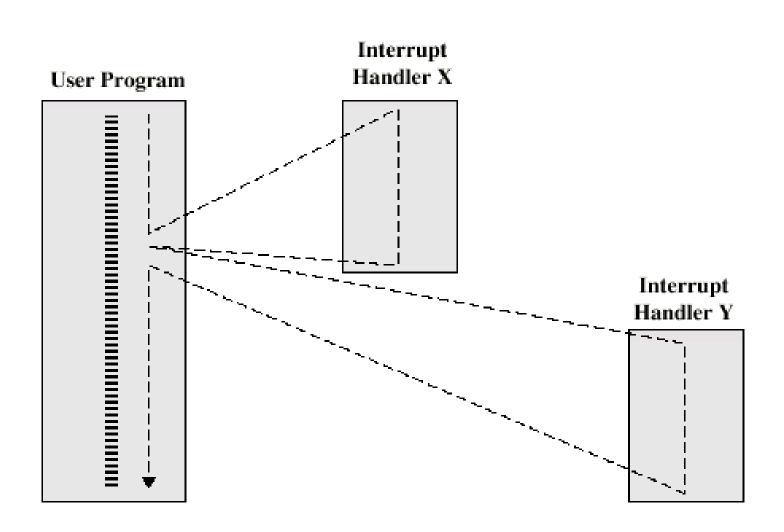

# Transferência de Controle via Interrupção

## Ciclo de Instrução com Interrupção

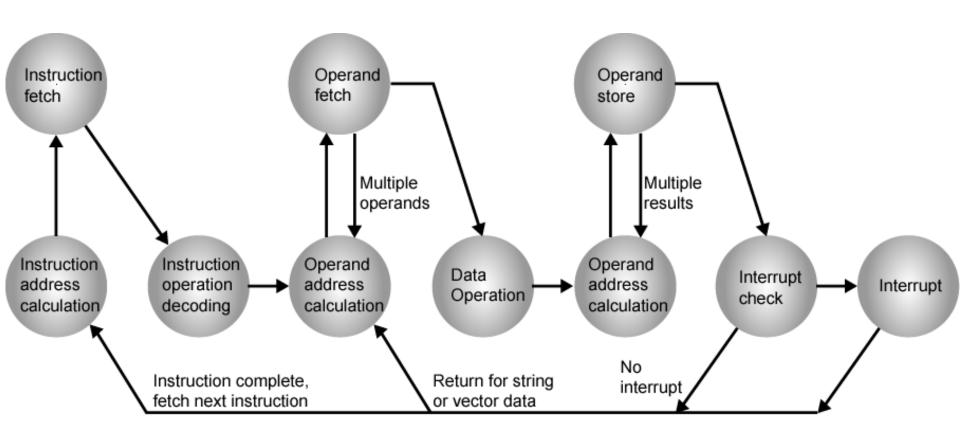

# Ciclo de Instrução (Com Interrupção) - Diagrama de Estado

### Multiplas Interrupções

- Desabilitar Interrupções

- Processador irá ignorar outras interrupções enquanto processa uma interrupção

- Interrupções se mantém pendentes e são verificadas após a primeira interrupção ser processada

- Interrupções são tratadas na sequência em que elas ocorrem

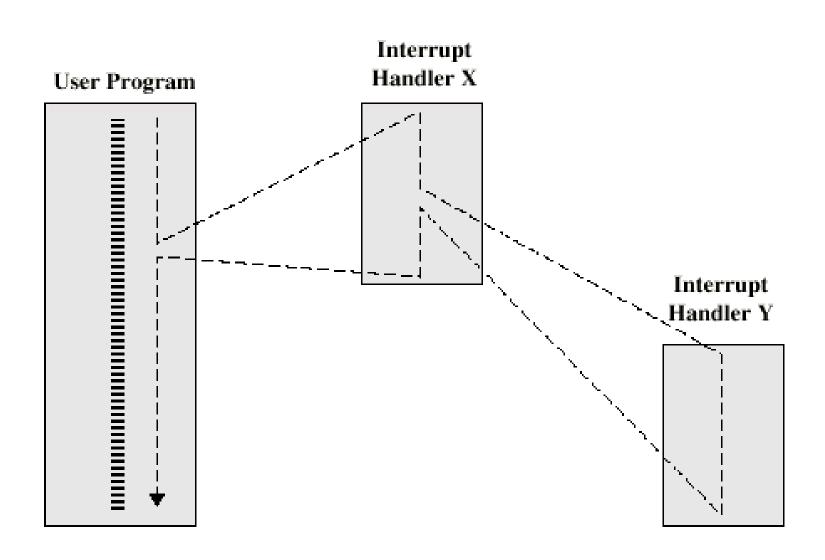

- Definir Prioridades

- Prioridades mais baixas podem ser interrompidas por prioridades mais altas

- Após a prioridade mais alta ser tratada, o processador retorna à interrupção anterior

## Multiplas Interrupções - Sequencial

# Multiplas Interrupções – Aninhado

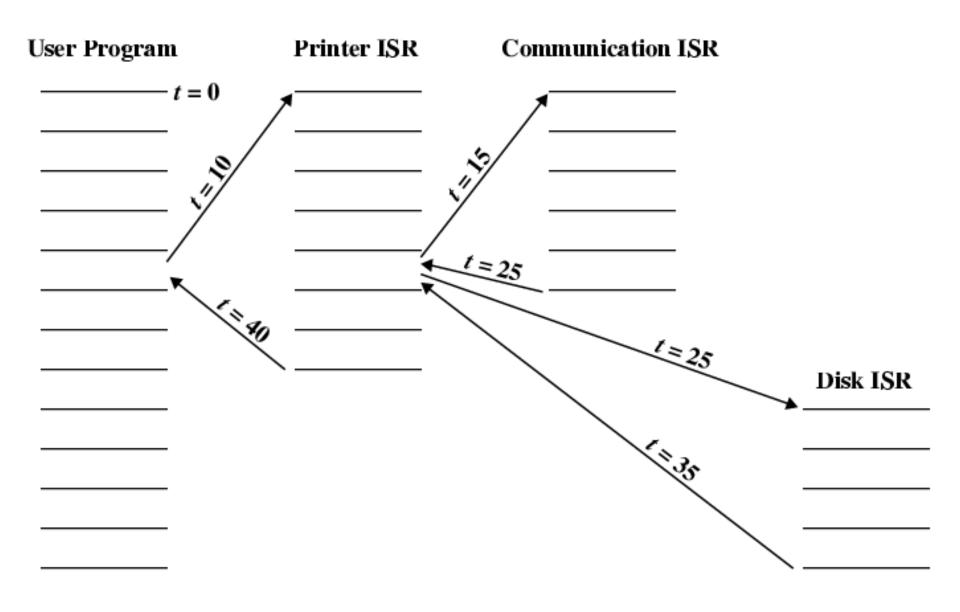

## Multiplas Interrupções - Sequência

Resolva, passo a passo, a sequência de Processamentos a seguir

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 8000 |

|-----|------|

| 951 | 0001 |

| 952 | 0004 |

#### Operações:

1 - Escrever no Acumulador

2 - Escrever na Memória

5-Soma

6 - Subtração

| PC |

|----|

| AC |

| IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 8000 |

|-----|------|

| 951 | 0001 |

| 952 | 0004 |

### Operações:

- 1 Escrever no Acumulador

- 2 Escrever na Memória

- 5 Soma

- 6 Subtração

| PC |

|----|

| AC |

| IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0001 |

| 952 | 0004 |

| 200  | PC |

|------|----|

|      | AC |

| 1950 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0001 |

| 952 | 0004 |

| 201  | PC |

|------|----|

| 8000 | AC |

| 1950 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0001 |

| 952 | 0004 |

| 201  | PC |

|------|----|

| 0008 | AC |

| 6951 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0001 |

| 952 | 0004 |

| 202  | PC |

|------|----|

| 0007 | AC |

| 6951 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0007 |

| 952 | 0004 |

| 203  | PC |

|------|----|

| 0007 | AC |

| 2951 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0007 |

| 952 | 0004 |

| 203  | PC |

|------|----|

| 0007 | AC |

| 5952 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0007 |

| 952 | 0004 |

| 204     | PC |

|---------|----|

| 0 0 0 B | AC |

| 6 9 5 1 | IR |

| 200 | 1950 |

|-----|------|

| 201 | 6951 |

| 202 | 2951 |

| 203 | 5952 |

| 204 | 6951 |

| 205 | 2952 |

| 950 | 0008 |

|-----|------|

| 951 | 0007 |

| 952 | 0004 |

| 205  | PC |

|------|----|

| 0004 | AC |

| 2952 | IR |

### Conexões

- Todas as unidades devem estar conectadas

- Diferentes tipos de conexões para diferentes tipos de unidades

- -Memória

- -E/S

- -CPU

### Módulos do Computador

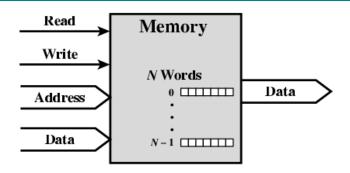

### Conexões de Memória

- Recebe e envia dados

- Recebe endereços

- Recebe sinais de controle

- -Leitura

- -Escrita

- —Temporizador

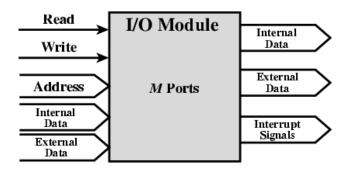

### Conexão E/S (1)

- Semelhante à memória do ponto de vista computacional

- Saída

- Recebe dados do computador

- Envia dados aos periféricos

- Entrada

- -Recebe dados dos periféricos

- Envia dados ao computador

### Conexão E/S (2)

- Recebe sinais de controle do computador

- Manda sinais de controle aos periféricos

- —Ex.: Mover o disco do HDD

- Receber endereço do computador

- —Ex.: Identificador do periférico

- Envia sinais de interrupção

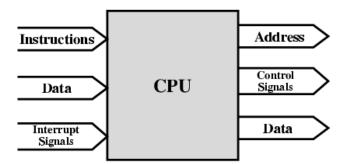

### Conexão CPU

- Lê dados e instruções

- Escreve dados após processamento

- Envia sinais de controle para as outras unidades

- Recebe e atua nas interrupções

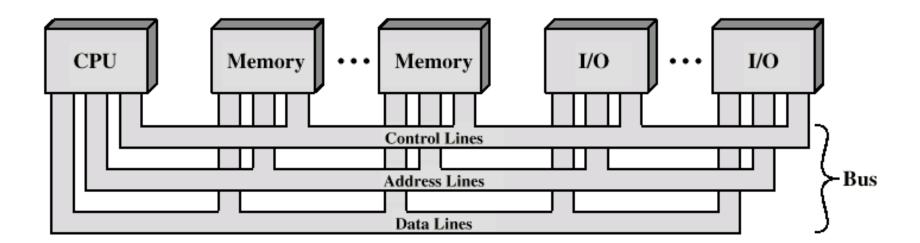

### **Barramentos - Buses**

- Existe uma quantidade possível de sistemas de interconexões

- Estrutura de barramento (BUS) (única ou múltipla) é o mais comum

- Ex.: Controle/Endereço/Dado (PC)

- Ex.: Unibus (DEC-PDP)

## O que é um barramento (bus) ?

- Um caminho de comunicação ligando dois ou mais dispositivos

- Frequentemente agrupado

- -Um número de canais em um barramento

- Ex.: Barramento de dados de 32 bit separados em canais de 1 bit

- Linhas de alimentação elétrica não são consideradas

#### **Barramento de Dados**

- Trafegam dados

- Nesse nível, não se diferenciam dados e instruções

- Largura é determinante para performance

- -8, 16, 32, 64 bit

## Barramento de Endereços

- Identificam a fonte ou o destino dos dados

- Ex.: CPU precisa ler uma instrução ou dado de uma dada posição da memória

- Largura do barramento determina a capacidada máxima do sistema

- —Ex.: 8080 tem barramento de endereços de 16 bit, oferencendo 64k de espaços de enderaçamentos (2<sup>16</sup> espaços de endereçamentos)

#### **Barramento de Controle**

- Informações de Controle e Temporizadores

- —Sinais de leitura/escrita de memória

- Requisição de interrupção

- —Sinais de Clock

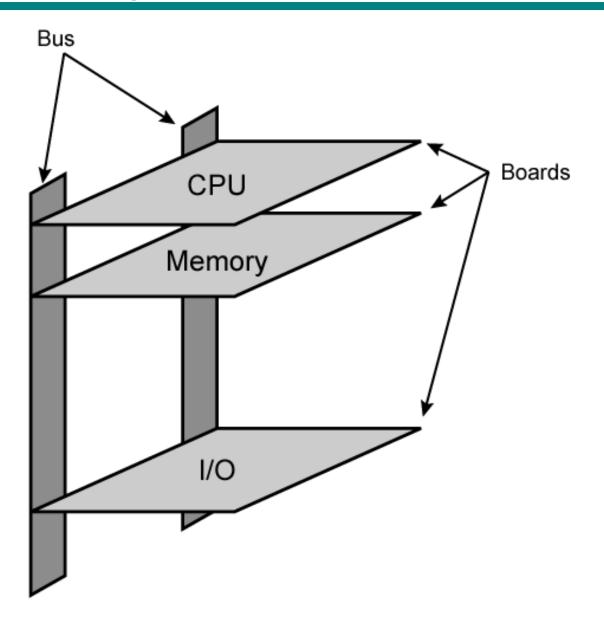

# Esquema de Interconexão de Barramentos

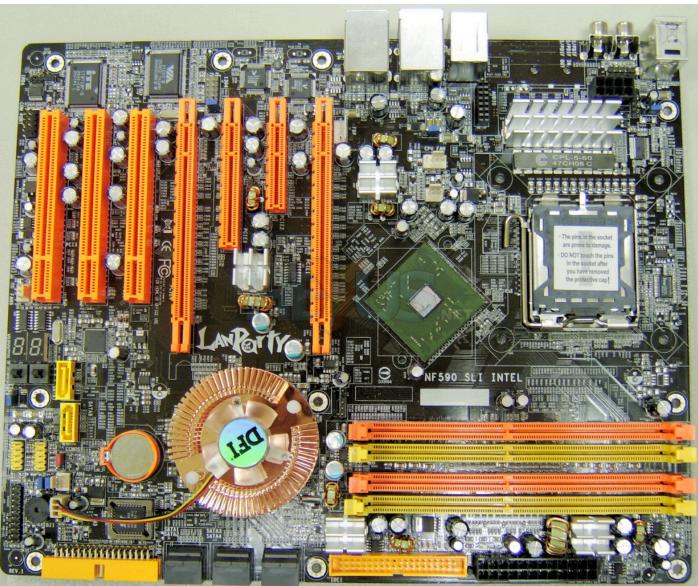

## Identificação

- Como um barramento se apresenta ?

- —Trilhas em placas de circuitos

- —Cabos flexíveis

- Conectores na placa mãe

- Ex.: PCI

- —Conjunto de cabos

## **Barramentos - Bus**

#### **Barramentos - Bus**

# Apresentação Física dos Barramentos

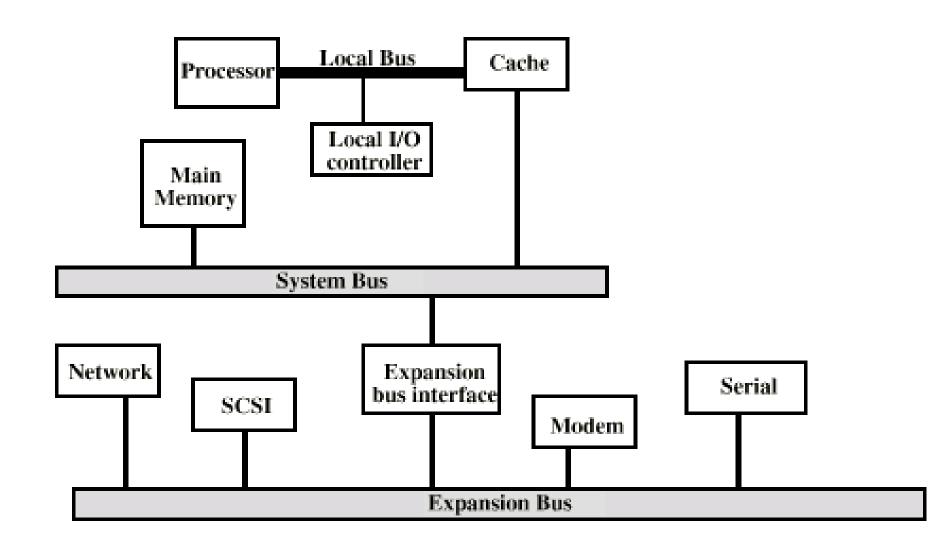

#### Problemas de Barramento Único

- Muitos dispositivos no mesmo barramento:

- Propagação de atrasos

- Longos caminhos para que os dados percorram significam que a coordenação do barraento pode levar a atrasos

- Maioria dos sistemas usam barramentos múltiplos para evitar esse problema

# Tradicional (ISA) (com cache)

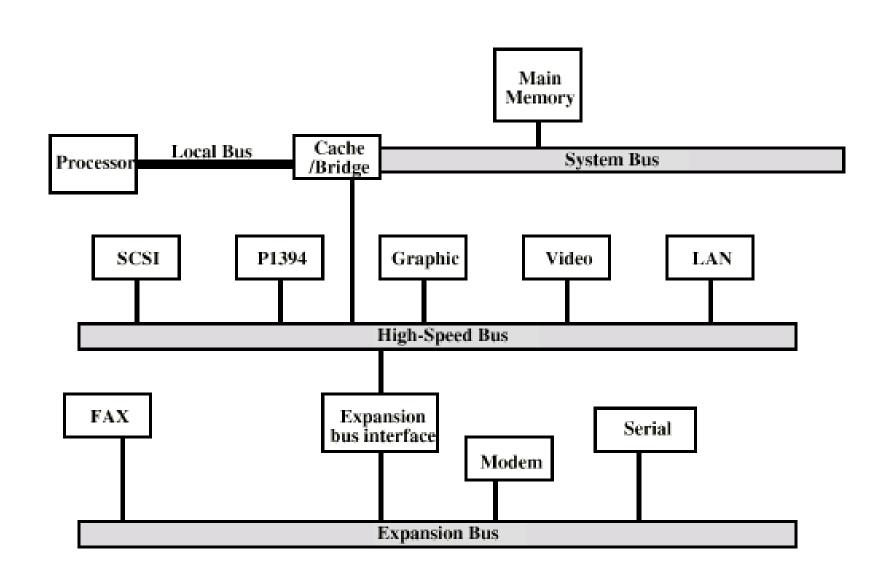

#### **Barramento de Alta Performance**

## **Tipos de Barramentos**

- Dedicados

- Linhas de dados e endereços separados

- Multiplexado

- -Compartilham linhas de dados e endereços

- Linhas de controle se mantém dedicadas

- Vantagem Menos linhas

- Desvantagem Controle mais complexo

## Arbitração de Barramento

- Mais de um dispositivo controlando o barramento

- Ex.: CPU e controlador DMA

- Somente um modulo pode controlar o barramento por vez

- Arbitração pode ser centralizada ou distribuida

## Arbitração centralizada ou distribuida

- Centralizada

- Um dispositivo de hardware controla o acesso ao barramento

- Controlador de Barramento

- —Pode ser parte da CPU ou separado

- Distribuido

- Cada modulo pode requisitar o barramento

- Controle lógico em todos os módulos

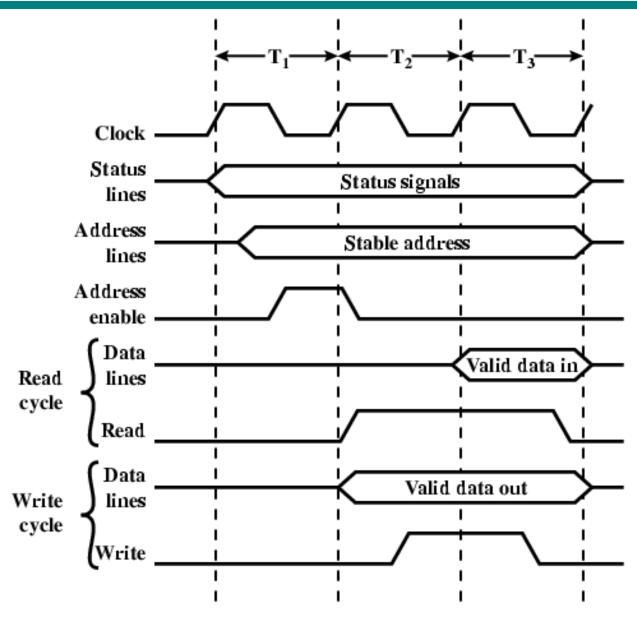

## **Temporizador**

- Coordenação de eventos no barramento

- Síncrono

- -Eventos determinados por sinais de controle

- —Barramento de controle inclui linha de clock

- —Um simples 1-0 é um ciclo de barramento

- —Todos os dispositivos podem ler a linha de clock

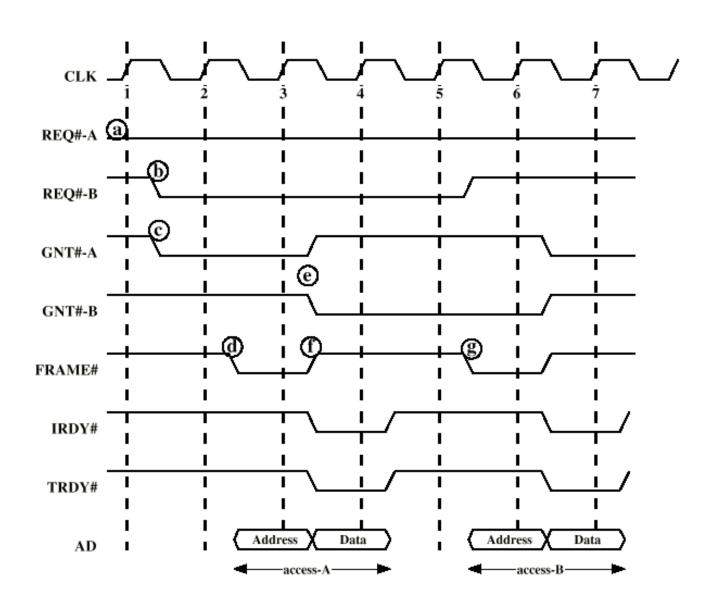

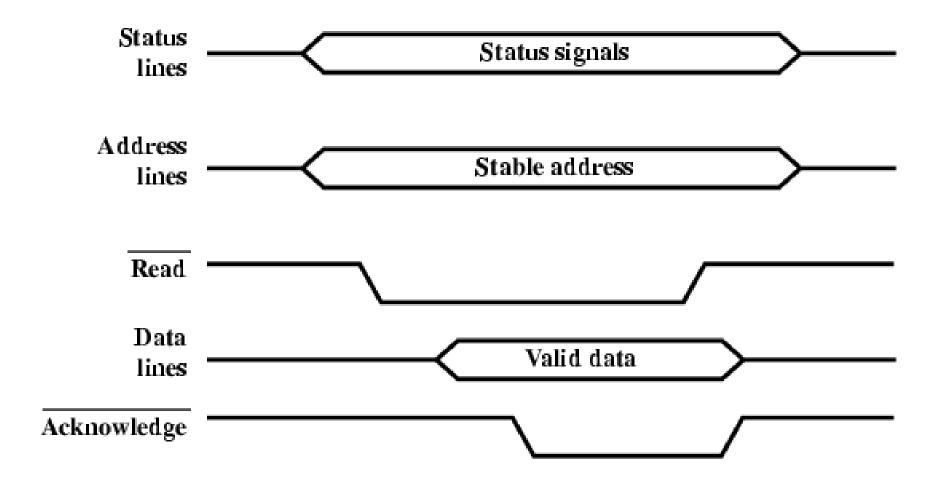

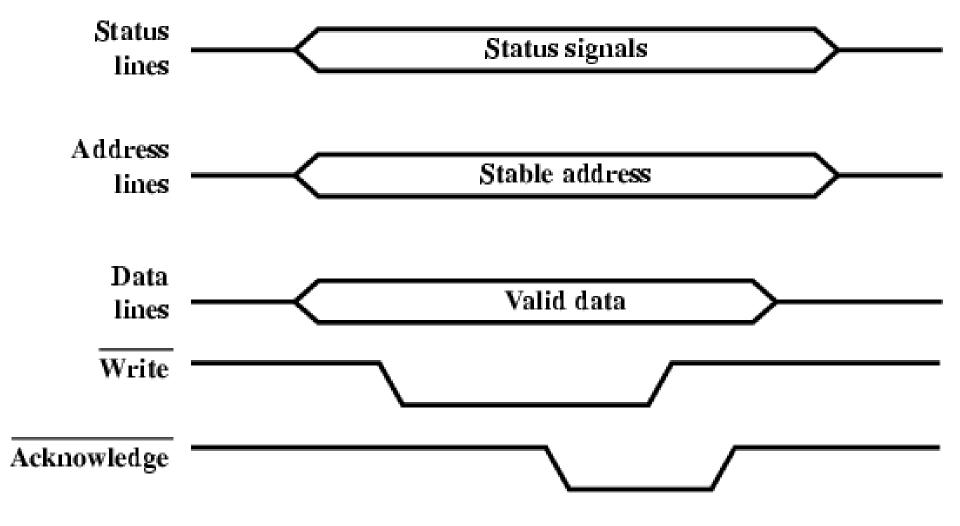

# Diagrama de temporizador síncrono

# Diagrama de temporizador assíncrono

# Diagrama de temporizador assíncrono

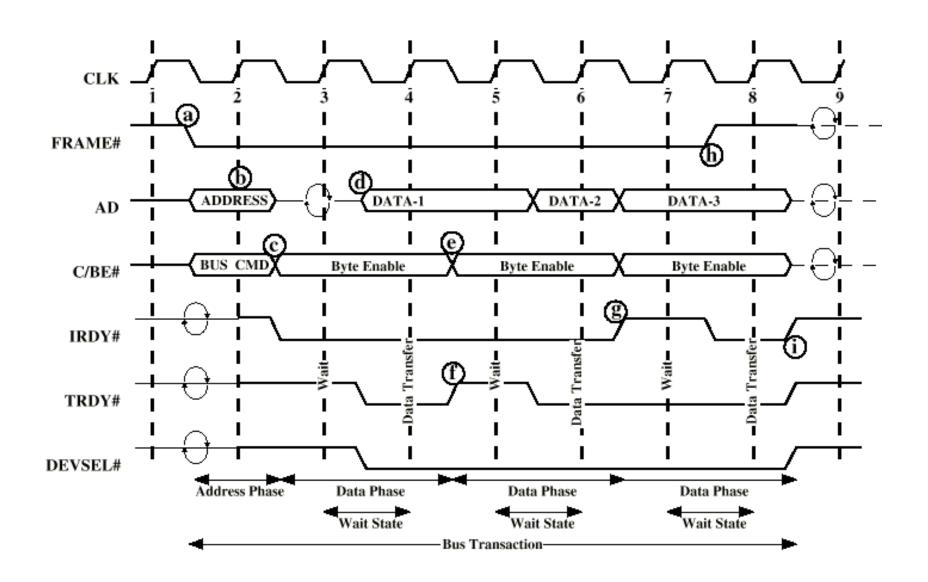

#### **Barramento PCI**

- Peripheral Component Interconnection

- Lançado pela Intel para domínio público

- 32 ou 64 bit

- 50 linhas

PCI - Ex

#### **Barramento PCI Bus - Linhas**

- Linhas de Sistema

- Inclui clock e reset

- Endereços & Dados

- —32 linhas mux para endereços/dados

- Linhas de interrupção e validação

- Controle de Interface

- Arbitração

- —Não compartilhada

- Conexão direta ao barramento PCI

- Linhas de Erro

#### **Barramento PCI Bus - Linhas**

- Linhas de Interrupção

- —Não compartilhada

- Suporte a Cache

- Extensão 64-bit

- -32 linhas adicionais

- Multiplexado síncrono

# Diagrama de leitura temporizada - PCI

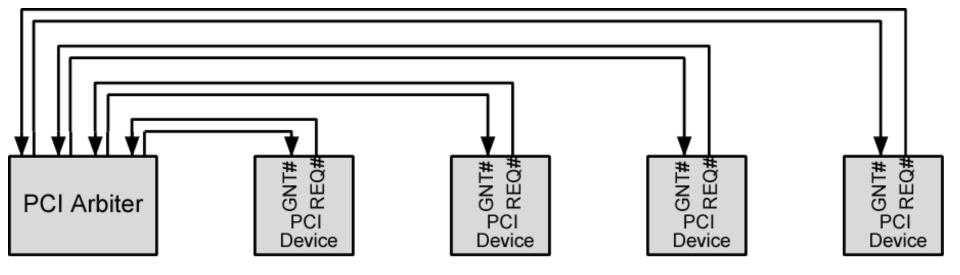

## **Árbitro de Barramento PCI**

# Arbitração de Barramento PCI